安然网9月3日消息,AMD下一代Zen 6架构的锐龙处理器将将分别采用台积电2nm和3nm工艺制造CCD和IOD。

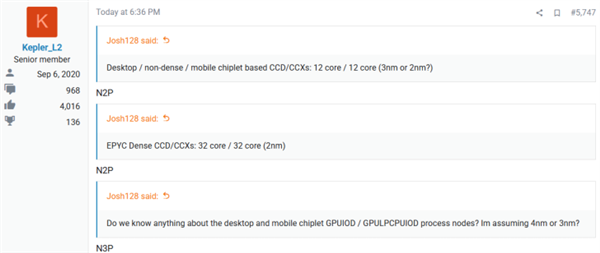

根据Kepler_L2最新透露,AMD下一代锐龙CPU将采用台积电N2P“2nm”工艺技术用于CCD(计算芯片),而IOD(输入/输出芯片)将采用台积电的N3P“3nm”工艺技术。

目前Zen 5架构的锐龙CPU的CCD采用4nm工艺,IOD则采用6nm工艺。

在Zen 6架构中,IOD将集成内存控制器、USB、PCIe等IO功能以及集成显卡;而CCD将包含Zen 6核心,每个CC包含12个核心、24个线程和48MB的L3缓存。

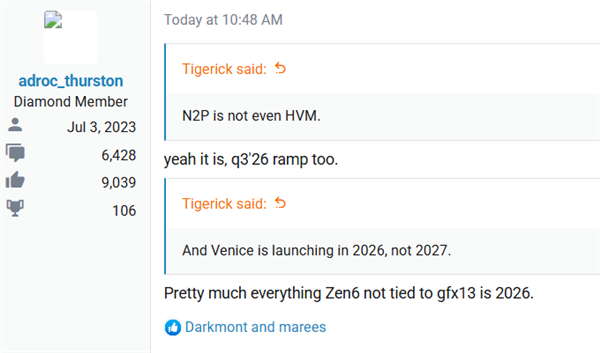

还有消息称,台积电N2P工艺将在2026年第三季度实现量产,这意味着最早可能在2026年第四季度或第三季度末看到基于Zen 6架构的下一代锐龙CPU。

而Intel的Nova Lake桌面CPU也将在类似的时间发布,不过与Intel不同的是,桌面CPU将继续支持现有的AM5平台。

– THE END –

评论0