十一长假前夕,Intel在美国亚利桑那州凤凰城举办了一场Tech Tour US技术之旅活动。

这也是继以色列(晶圆厂)、马来西亚(封装厂)、中国台北(电脑展)之后,第四次此类活动。

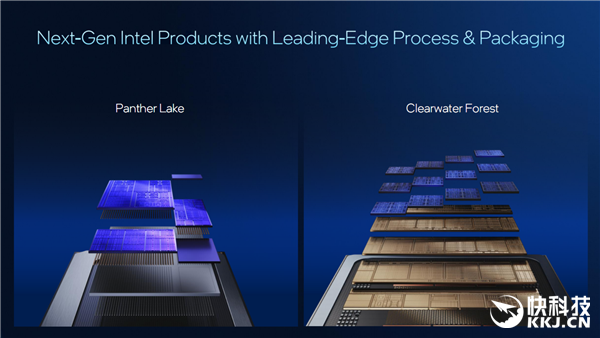

活动期间,我们参观了位于凤凰城的Fab 42/52晶圆厂,还提前了解了下一代酷睿Ultra处理器Panther Lake、下一代至强6+处理器Clearwater Forest的架构与技术细节,现在和大家分享!

首先强调一点,Panther Lake、Clearwater Forest此次解密的仅限架构设计、技术特性,而产品型号、规格参数、性能表现将在后续正式发布的时候公开。

【Intel 18A工艺与先进封装:四季度量产】

Panther Lake、Clearwater Forest是首个采用Intel 18A工艺的量产产品,这也是在美国本土最先进的制程工艺。

Intel 18A的技术特性之前已经讲了多次,如今量产在即,再做一次简单的回顾总结。

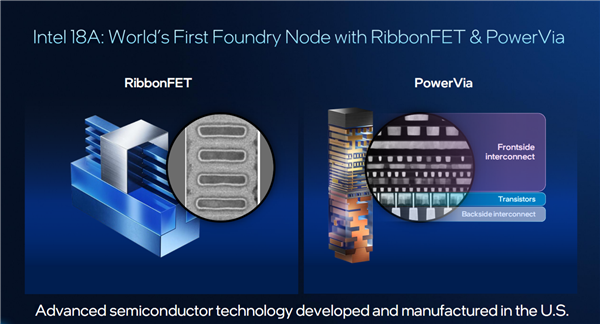

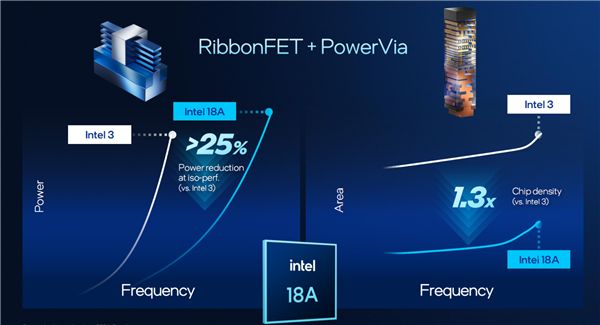

Intel 18A标志着半导体制程工艺的一次重大突破,尤其是它首次加入了两大全新革命性技术:RibbonFET全环绕晶体管、PowerVia背部供电。

二者结合,彻底颠覆了多年来的晶体管与晶圆结构,奠定了Intel称之为“埃米时代”的基础,在密度、性能、能效等各方面都带来了显著变化。

RibbonFET其实是GAA全环绕晶体管结构的一种实现方式,台积电、三星也都有类似的技术,但具体设计各有各的特色。

RibbonFET采用4条垂直堆叠的纳米带(Nano Ribbons)结构,使得栅极能够完全包围沟道,再加上沟道结构和栅极控制的优化,相比传统FinFET立体晶体管结构,驱动电流可增强20%,晶体管开关速度可提升15%。

同时,它还能有效减少漏电现象,支持八个不同的逻辑阈值电压,芯片设计也可以更加灵活。

另外,RibbonFET还融入了Intel的诸多工艺创新,包括全新的栅极光刻工艺、功函数工程优化、短沟道效应控制等等。

PowerVia背部供电就比较好理解了,就是将传统上位于晶圆正面的供电电路,转移到背面,这可是Intel独有的,也是第一家投入量产的,台积电和三星都不具备。

多年来,晶圆设计都是将信号线(Signal)、供电线(Power)混合分布在晶体管之上,也就是晶圆的正面,但随着晶体管尺寸不断缩小,信号线、供电线布线越来越拥挤,功耗能效、信号干扰等问题越来越凸显。

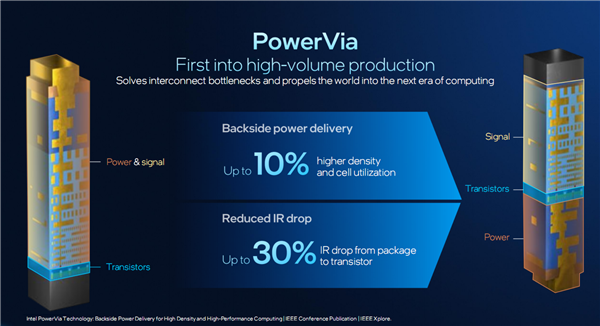

PowerVia将供电层移至晶体管或者说晶圆的背面,并在每个标准单元中嵌入纳米级硅通孔(nano TSV),从而实现了供电线与信号线的分离,晶体管的供电路径变得更加直接高效。

这么做可以大大提高供电效率,减少损耗,降低芯片整体功耗;

可以有效减少压降(IR Drop)最多达30%,提升芯片运行频率最多6%;

可以减少甚至消除信号干扰,实现更好的信号完整性;

可以提升标准单元利用率最多达10%,进一步提高晶体管密度。

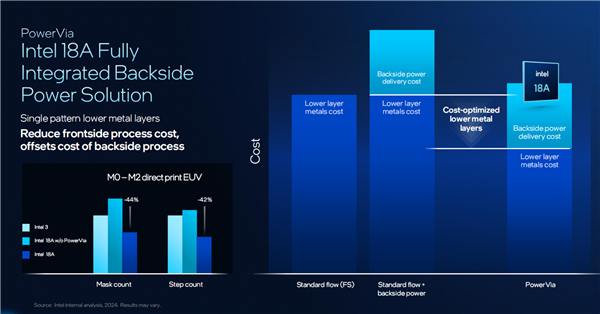

当然,单纯使用背部供电,成本会显著增加,但是Intel PowerVia是一个完整方案,同时还有一系列配套优化,包括减少金属层、遮罩数量、工序步骤,以及精简正面工艺等等,使得综合成本显著低于传统正面供电工艺。

按照Intel给出的数据,同样是M0-M2金属层直接印刷EUV工艺,PowerVia加持的Intel 18A对比Intel 3,遮罩数量减少了44%,工序步骤减少了42%。

RibbonFET、PowerVia两大变革结合,使得Intel 18A对比Intel 3综合能效提升最多15%、同等性能下功耗降低最多25%、芯片密度提升30%。

当然,这些指标只是工艺层面的,落实到处理器产品层面还要结合架构、规格的变化。

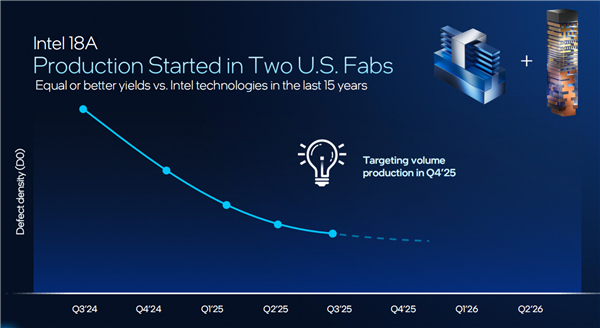

对于大家非常关心的18A量产进度,Intel也给出了明确的时间表。

目前,18A早在2024年第三季度就已经投入试产,目前正在美国亚利桑那州、俄勒冈州两地的工厂积极推进,缺陷密度不断降低,计划量产时间是今年第四季度,正好和Panther Lake的发布计划相符合。

Intel还强调,18A的良品率和Intel过往15年的工艺水平基本相当,甚至更好一些。

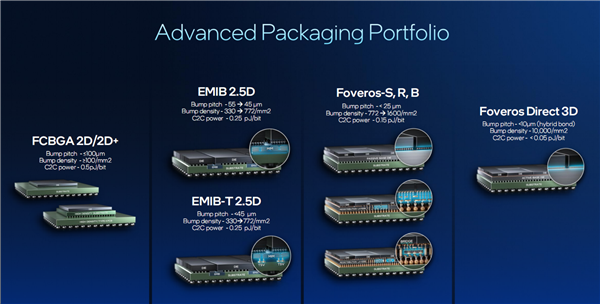

除了先进工艺,Intel还有着丰富的先进封装技术,可以分为EMIB、Foveros两大家族,各自又衍生出了不同的版本,满足不同的封装需求。

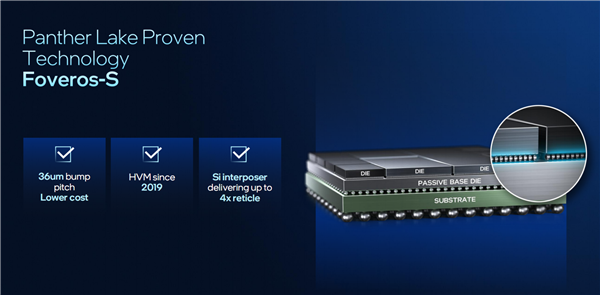

Panther Lake就使用了2019年便已量产、久经考验的Foveros-S 2.5D封装技术,结合EMIB,将不同模块(Die)堆叠封装在一个被动无源基础模块之上,实现高效互联互通,方便灵活放大或缩小规模,而且成本可控。

– THE END –

评论0